Bachelor-Arbeiten

Student*in: Benedikt Heumüller

Betreuer*in: Changgong Li

Zeitraum: 10.06.2013 - 09.09.2013

Ziel dieser Arbeit soll es sein, eine Integer-ALU auf Basis des bestehenden Prozessormodells auf einem FPGA in Verilog zu implementieren. Dabei soll die Anzahl der benutzten Pipeline-Stufen mit einem Parameter festgelegt werden können. Die dadurch entstehende ALU soll dann alle Integer-Operationen ausführen können, welche durch das AMIDAR Modell definiert sind.

Student*in: Alexander Weisel

Betreuer*in: Changgong Li

Zeitraum: 29.07.2013 - 28.10.2013

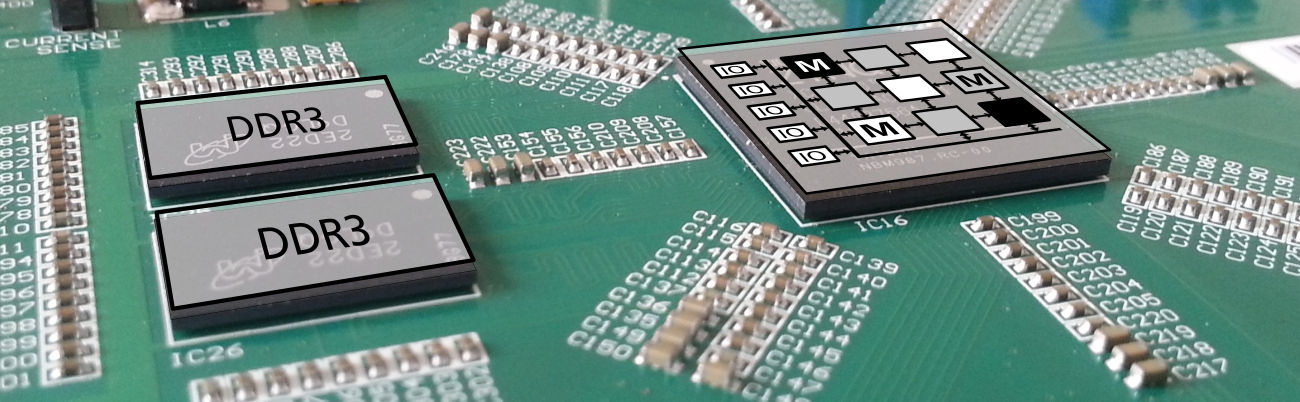

Bisher wird das erstelle SoC jedoch nur in Form eines Baums in der GUI von jConfig dargestellt, wodurch bei umfangreicheren Projekten leicht die Übersicht verloren gehen kann. Deshalb soll im Rahmen dieser Arbeit eine grafische Visualisierung des SoCs in jConfig integriert werden, die dem Anwender einen Überblick über alle integrierten Hardware-Module und deren Verbindungen liefert.

Student*in: Rainer Wahler

Betreuer*in: Prof. Dr. Christian Hochberger

Zeitraum: 15.02.2013 - 24.05.2013

Am Beispiel einer so genannten Zeitwaage (Wikipedia) soll dieser Entwurfszyklus exemplarisch komplett durchlaufen werden (von der Bauteilauswahl, über das Platinendesign, bis zu Inbetriebnahme und Programmierung).

Master-Arbeiten

Student*in: Ammar Obaid

Betreuer*in: Prof. Christian Hochberger/extern

Zeitraum: 15.02.2013 - 14.08.2013

- Implementation of a tool for code instrumentation. The tool can either work on source or on object level. It should be developed on the basis of existing tools.

- Application of this tool to generate instrumentation that uses the ITM (Instrumentation Trace Macrocell) of Cortex M3 processors to compute the code coverage of an application

- Application of the tool to generate a different instrumentation that does not require the ITM, but rather uses regular code trace features on a Cortex R4

- Evaluation of the overhead of both methods. For this purpose sample applications have to be implemented on both platforms. These sample applications should span the range from completely control flow dominated code to completely computation dominated code.

Student*in: Frédéric Peignet

Betreuer*in: Prof. Dr. Christian Hochberger

Zeitraum: 11.02.2013 - 09.08.2013

Die QorIQ P4080 Prozessoren der Firma Freescale liefern ihre Trace-Daten über die Aurora-Schnittstelle nach außen. Die Aurora-Schnittstelle besteht aus einer konfigurierbaren Zahl von High-Speed Serial Links (bis ca. 5Gb/s).

Aufgaben:

- Inbetriebnahme der Trace-/Debug-Einheit im QorIQ P4080 Prozessor

- Implementierung einer Aurora-Schnittstelle in einem FPGA, um Trace-Daten entgegen nehmen zu können

- Erweiterung der Nexus-Implementierung, um empfangene Trace-Daten auswerten zu können